### RACAL INSTRUMENTS 7064M MESSAGE BASED PROTOTYPE MODULE

**PUBLICATION NO. 980820**

EADS North America Defense Test and Services, Inc. 4 Goodyear, Irvine, CA 92618 Tel: (800) 722-2528, (949) 859-8999; Fax: (949) 859-7139

> info@eads-nadefense.com sales@eads-nadefense.com helpdesk@eads-nadefense.com http://www.eads-nadefense.com

### PUBLICATION DATE: October 07, 2002

Copyright 1998 by EADS North America Defense Test and Services, Inc. Printed in the United States of America. All rights reserved. This book or parts thereof may not be reproduced in any form without written permission of the publisher.

### THANK YOU FOR PURCHASING THIS EADS NORTH AMERICA DEFENSE TEST AND SERVICES PRODUCT

For this product, or any other EADS North America Defense Test and Services, Inc. product that incorporates software drivers, you may access our web site to verify and/or download the latest driver versions. The web address for driver downloads is:

http://www.eads-nadefense.com/downloads

If you have any questions about software driver downloads or our privacy policy, please contact us at:

info@eads-nadefense.com

### WARRANTY STATEMENT

All EADS North America Defense Test and Services, Inc. products are designed and manufactured to exacting standards and in full conformance to EADS ISO 9001:2000 processes.

For the specific terms of your standard warranty, or optional extended warranty or service agreement, contact your EADS North America Defense Test and Services, Inc. customer service advisor. Please have the following information available to facilitate service.

- 1. Product serial number

- 2. Product model number

- 3. Your company and contact information

You may contact your customer service advisor by:

| E-Mail:    | Helpdesk@eads-nadefense.com |       |

|------------|-----------------------------|-------|

| Telephone: | +1 800 722 3262             | (USA) |

| Fax:       | +1 949 859 7309             | (USA) |

### **RETURN of PRODUCT**

Authorization is required from EADS North America Defense Test and Services, Inc. before you send us your product for service or calibration. Call or contact the Customer Support Department at 1-800-722-3262 or 1-949-859-8999 or via fax at 1-949-859-7139. We can be reached at: <u>helpdesk@eads-nadefense.com</u>.

### **PROPRIETARY NOTICE**

This document and the technical data herein disclosed, are proprietary to EADS North America Defense Test and Services, Inc., and shall not, without express written permission of EADS North America Defense Test and Services, Inc., be used, in whole or in part to solicit quotations from a competitive source or used for manufacture by anyone other than EADS North America Defense Test and Services, Inc. The information herein has been developed at private expense, and may only be used for operation and maintenance reference purposes or for purposes of engineering evaluation and incorporation into technical specifications and other documents which specify procurement of products from EADS North America Defense Test and Services, Inc.

### DISCLAIMER

Buyer acknowledges and agrees that it is responsible for the operation of the goods purchased and should ensure that they are used properly and in accordance with this handbook and any other instructions provided by Seller. EADS North America Defense Test and Services, Inc. products are not specifically designed, manufactured or intended to be used as parts, assemblies or components in planning, construction, maintenance or operation of a nuclear facility, or in life support or safety critical applications in which the failure of the EADS North America Defense Test and Services, Inc. product could create a situation where personal injury or death could occur. Should Buyer purchase EADS North America Defense Test and Services, Inc., its officers, employees, subsidiaries, affiliates and distributors harmless against all claims arising out of a claim for personal injury or death associated with such unintended use.

### FOR YOUR SAFETY

Before undertaking any troubleshooting, maintenance or exploratory procedure, read carefully the **WARNINGS** and **CAUTION** notices.

CAUTION RISK OF ELECTRICAL SHOCK DO NOT OPEN

This equipment contains voltage hazardous to human life and safety, and is capable of inflicting personal injury.

If this instrument is to be powered from the AC line (mains) through an autotransformer, ensure the common connector is connected to the neutral (earth pole) of the power supply.

Before operating the unit, ensure the conductor (green wire) is connected to the ground (earth) conductor of the power outlet. Do not use a two-conductor extension cord or a three-prong/two-prong adapter. This will defeat the protective feature of the third conductor in the power cord.

Maintenance and calibration procedures sometimes call for operation of the unit with power applied and protective covers removed. Read the procedures and heed warnings to avoid "live" circuit points.

Before operating this instrument:

- 1. Ensure the proper fuse is in place for the power source to operate.

- 2. Ensure all other devices connected to or in proximity to this instrument are properly grounded or connected to the protective third-wire earth ground.

If the instrument:

- fails to operate satisfactorily

- shows visible damage

- has been stored under unfavorable conditions

- has sustained stress

Do not operate until, performance is checked by qualified personnel.

### **EC Declaration of Conformity**

| We                                            |                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4 Go                                          | al Instruments Inc.<br>odyear Street<br>e, CA 92718                                                                                                                                                                                                                                                                                                                                                                         |

| declare und                                   | er sole responsibility that the                                                                                                                                                                                                                                                                                                                                                                                             |

| 7064<br>7064<br>7064<br>7064<br>7064          | M 1S Msg Based Prototype Module, P/N 407620-100<br>M 2S Msg Based Prototype Module, P/N 407620-200<br>M 3S Msg Based Prototype Module, P/N 407620-300<br>M 1S Msg Based Prototype No Intf., P/N 407620-101<br>M 2S Msg Based Prototype No Intf., P/N 407620-201<br>M 3S Msg Based Prototype No Intf., P/N 407620-201<br>M 3S Msg Based Prototype No Intf., P/N 407620-301<br>05 Msg Based Interface Module P/N 407620-OPT05 |

| conform to t                                  | the following Product Specifications:                                                                                                                                                                                                                                                                                                                                                                                       |

| Safety:                                       | EN 61010-1:1993+A2:1995                                                                                                                                                                                                                                                                                                                                                                                                     |

| EMC:                                          | EN 61326:1997+A1:1998,CLASS A                                                                                                                                                                                                                                                                                                                                                                                               |

| The a<br>in a<br>insta<br>The<br>Low<br>89/33 | htary Information:         above specifications are met when the product is installed         Racal Instruments certified mainframe with faceplates         lled over all unused slots, as applicable.         product herewith complies with the requirements of the         Voltage Directive 73/23/EEC and the EMC Directive         36/EEC.         March 5, 2002       Karm Karen Evensen                              |

|                                               | Director of Engineering                                                                                                                                                                                                                                                                                                                                                                                                     |

This page was left intentionally blank.

### **Table of Contents**

| Chapter 1              | 1-1 |

|------------------------|-----|

| GENERAL DESCRIPTION    | 1-1 |

| What's In This Chapter | 1-1 |

| Introduction           | 1-1 |

| General Description    | 1-2 |

| 7064M Specifications   | 1-5 |

| Chapter 2                                        | 2-1 |

|--------------------------------------------------|-----|

| INSTALLATION INSTRUCTIONS                        | 2-1 |

| What's In This Chapter                           | 2-1 |

| Unpacking and Inspection                         | 2-1 |

| VXIbus Logical Address Switch                    | 2-2 |

| VXIbus Interrupt Handler Setting                 | 2-3 |

| 7064M to VXIbus Mainframe Installation           | 2-3 |

| Power-Up Self-Test Initialization                | 2-4 |

| Self-Test                                        | 2-5 |

| Board ID Check                                   | 2-5 |

| Port Initialization                              | 2-5 |

| VXIbus Interface Initialization                  | 2-5 |

| Local Bus Usage with 7064M Breadboard            | 2-5 |

| Slave Module with 7064M Master Module            | 2-6 |

| Bus Grant and Local Bus Jumpers                  | 2-7 |

| Installing the VXI <i>plug&amp;play</i> Software | 2-8 |

| Chapter 3                                      | 3-1  |

|------------------------------------------------|------|

| JSING THE BREADBOARD                           | 3-1  |

| What's In This Chapter                         | 3-1  |

| Module Cooling Considerations                  |      |

| Calculated Module Operating Point              |      |

| DC Voltages Available to Prototyping Area      | 3-3  |

| Local Bus Interface                            |      |

| TTL Trigger Lines                              |      |

| Miscellaneous VXI Signals                      | 3-5  |

| I/O Port Write Strobes                         | 3-5  |

| Input/Output Ports                             |      |

| Controlling the I/O Ports                      |      |

| Output Port Reset Polarity                     | 3-8  |

| I/O Port Configuration                         |      |

| I/O Port Control                               | 3-8  |

| Module Address Switch                          |      |

| Port Addressing Schemes                        | 3-11 |

| Base Numbers                                   |      |

| Local Command Set                              |      |

| Command Syntactic Style                        |      |

| Command Overview                               |      |

| Output Format Command                          |      |

| Port I/O Bit Commands                          | 3-13 |

| Port I/O Byte Commands                         | 3-13 |

| Port I/O Word Commands – Two Consecutive Ports |      |

| Trigger Commands            | 3-14 |

|-----------------------------|------|

| Scanlist Commands           | 3-15 |

| Non-Vol Management Commands | 3-17 |

| Timer Management Commands   | 3-17 |

| Memory Management Commands  | 3-18 |

| Output Format Commands      | 3-18 |

| IEEE-488.2 Commands         | 3-18 |

| Command Reference           | 3-22 |

# Chapter 4 4-1 PRODUCT SUPPORT 4-1 Product Support 4-1 Warranty 4-1

| Appendix A       | A-1 |

|------------------|-----|

| 68000 INTERFACE  | A-1 |

| Introduction     | A-1 |

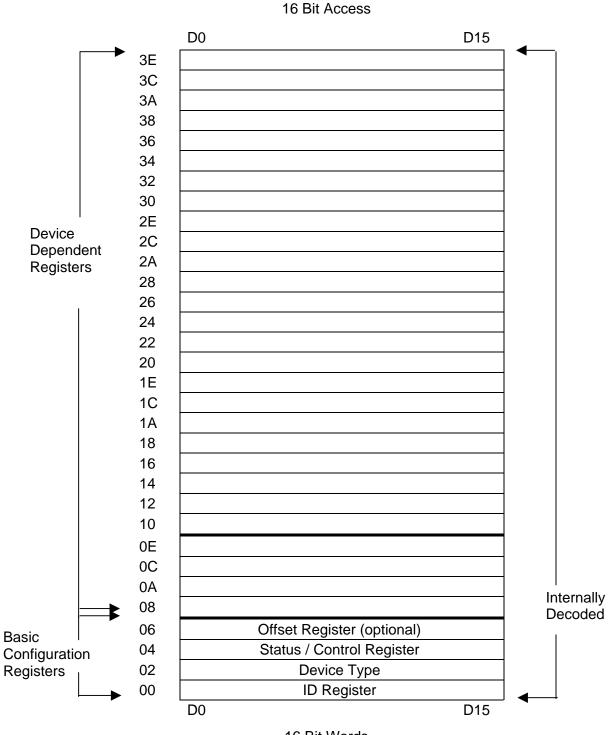

| VXIbus Interface | A-1 |

| Timer            | A-1 |

| Memory Space     | A-2 |

### List of Figures

| Figure 1-1, 7064M Message Based Front Panel | .1-2 |

|---------------------------------------------|------|

| Figure 1-2, 7064M Message-Based Breadboard  | .1-3 |

|                                             |      |

| Figure 2-2, Installa | ation of Bus Grant Jum | per and Local Bus Jump | er2-7 |

|----------------------|------------------------|------------------------|-------|

Figure 2-1, VXIbus Logical Address Switch......2-2

| Figure 3-1, 7064M Message-Based Breadboard          | 3-1  |

|-----------------------------------------------------|------|

| Figure 3-2, Card Address Switch                     | 3-10 |

| Figure 3-3, Standard Status Data Structure Overview | 3-21 |

### List of Tables

| Table 1-1, VXI Interface                         | .1-5 |

|--------------------------------------------------|------|

| Table 1-2, 7064M Module Power                    | .1-6 |

| Table 1-3, Breadboard Area Specification         | .1-6 |

| Table 1-4, Cooling Requirements                  | .1-7 |

| Table 1-5, 7064M Mechanical Parameters           | .1-7 |

| Table 1-6, 7064M Environmental Specifications    | .1-7 |

| Table 1-7, Reliability and Safety Specifications | .1-8 |

| Table 1-8, EMC Specifications                    | .1-8 |

| Table1-9, Option Table                           | .1-9 |

Table 2-1, Signal Shorts For Chassis With Auto-Configuration P1 Connectors ......2-4

| Table 3-1, DC Voltages Available to Prototyping Area  | . 3-3 |

|-------------------------------------------------------|-------|

| Table 3-2, VXI Signals                                | . 3-4 |

| Table 3-3, VXI TTL Trigger Lines                      | . 3-5 |

| Table 3-4, Miscellaneous Signals                      | . 3-5 |

| Table 3-5, I/O Port Write Strobes                     | . 3-6 |

| Table 3-6, I/O Port Description for Port 0 to Port 11 | . 3-6 |

| Table 3-7, I/O Port Control                           | . 3-9 |

| Table 3-8, Card Address Switch                        | 3-10  |

This page was left intentionally blank.

### Chapter 1 GENERAL DESCRIPTION

### What's In This Chapter

- Introduction

- General Description of the 7064M

- 7064M Specifications

- 7064M Options Table

### Introduction

This manual contains information on how to install and operate the 7064M in a VXIbus environment. It describes the functions and applications of the 7064M Message Based Prototype.

Figure 1-1, 7064M Message Based Front Panel

### General Description

The 7064M-100, -200, and -300 are "master" message-based VXIbus development cards made up of a removable message-based interface and a breadboard card for prototyping and developing of digital and analog circuits. The 7064M-101, -201, and -301 "slave" VXIbus development cards consist of the breadboard card only (omitting the removable message-based interface card).

Eighty-two square inches of breadboard real estate are available to the user, along with all the appropriate VXIbus backplane signals. The user circuitry in the breadboard area is controlled through twelve 8-bit individually configurable ports located on the breadboard card. The user circuitry can also be controlled through the message-based module's 68000 micro controller directly if Option 95, Source Code is purchased (P/N 407620-Opt95) The upper half of the 68000 address space is available for this purpose.

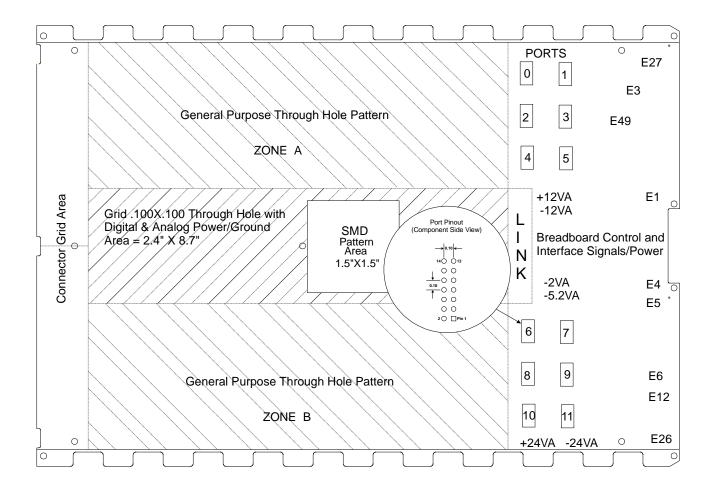

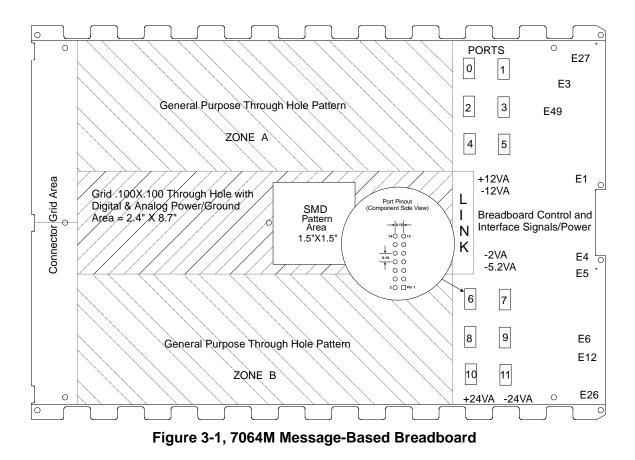

The development area consists of five separate areas to provide maximum flexibility and utilization. Refer to **Figure 1-2** and the description on the following page:

Figure 1-2, 7064M Message-Based Breadboard

- **Universal grid area** Universal array with 0.1 inch center hole pattern allows placement of large grid arrays.

- General-purpose through-hole pattern area Rows of holes based on 0.1 grid allow placement of the standard DIP packages and de-coupling capacitors. There are two uncommitted power distribution planes in each zone (A and B) available to the user. These uncommitted planes (referred to as "Top" and "Bottom") may be connected to various power supplies provided by the VXI backplane. Connections to the +5V Power, Ground, and "Top" and "Bottom" planes are placed along the DIP rows for convenient connection.

- **SMD pattern area** Multipurpose pattern can accommodate the following combination of Plastic Leaded Chip Carrier (PLCC) and Small Outline (SO) Surface Mount Devices:

- a) PLCC-68 (1 each)

- b) PLCC-44 (1 each)

- c) PLCC-32 (1 each) + PLCC-20 (1 each) + SO-20L (2 each)

- d) PLCC-28 (1 each) + PLCC-20 (1 each) + SO-20L (2 each)

- **Connector grid area** A universal array with 0.1 inch center hole pattern is provided for the easy placement of interface connectors, and has enough mounting holes to accommodate high-density connectors.

All seven VXIbus supply lines are available to the user and are fused, reducing the risk of damage to the backplane. The 7064M module also provides the EMI power filtering required by the VXIbus specifications, removing the need for the user to design this circuitry.

The 7064M is available in single, double, or triple slot versions (-10X, -20X, -30X).

### 7064M Specifications

| Characteristics                                   | Description                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VXI Interface Capabilities                        | VXIbus Specification Rev 1.4 compliant<br>Message-Based Device<br>A16, A16/24<br>Servant only<br>Static or Dynamic Configuration<br>Instrument Protocol (I)<br>IEEE-488.2 Instrument Protocol (I4)<br>Programmable Interrupter<br>Event Generator<br>Response Generator<br>Trigger input interrupts CPU<br>Trigger output under CPU control |

| VXI Plug&Play Support                             | Fully Compliant                                                                                                                                                                                                                                                                                                                             |

| Software Protocols supported by VXI Interface     | IEEE 488.2 common commands (for I4 instrument)                                                                                                                                                                                                                                                                                              |

| Device Dependent Registers/<br>Shared Memory      | Shared RAM configured as A24 Shared Memory                                                                                                                                                                                                                                                                                                  |

| Annunciators (Front Panel)<br>FAIL<br>ACCESS      | Failed LED, Refer to VXIbus Spec 1.4 for definition.<br>Indicates VXI A16/A24 access.                                                                                                                                                                                                                                                       |

| CPU                                               | 16 MHz 68000                                                                                                                                                                                                                                                                                                                                |

| Memory<br>RAM<br>ROM<br>Non-vol RAM<br>Shared RAM | 32K X 16<br>64K X 16<br>8K X 16<br>32K X 16 (see Device Dependent Registers/ Shared<br>Memory above)                                                                                                                                                                                                                                        |

| Interface Connection<br>CPU Port                  | Full access to CPU address (A23-A1), data (D15-D0) and control lines at P100.                                                                                                                                                                                                                                                               |

| Shared Memory Port                                | Full access to VXI ASIC Shared Memory address (SA23-SA1), data (SD15-SD0), and control lines at P103 connector.                                                                                                                                                                                                                             |

### Table 1-1, VXI Interface

| Characteristic                     |         | Description                               |

|------------------------------------|---------|-------------------------------------------|

| DC Current (I <sub>PM</sub> )      | Voltage | I <sub>PM</sub> (Steady-State<br>Current) |

|                                    | +5V     | 1.25A                                     |

| Dynamic Current (I <sub>dM</sub> ) | Voltage | I <sub>dM</sub> (mAmps <sub>pp</sub> )    |

|                                    | +5V     | 10.0                                      |

### Table 1-2, 7064M Module Power

### Table 1-3, Breadboard Area Specification

| Characteristics                                 | Description                                                               |

|-------------------------------------------------|---------------------------------------------------------------------------|

| Maximum User Current                            | Specification                                                             |

| +5V                                             | 5 Amps Max                                                                |

| -5.2V                                           | 5 Amps Max                                                                |

| -2V                                             | 2 Amps Max                                                                |

| +12V                                            | 1 Amp Max                                                                 |

| -12V                                            | 1 Amp Max                                                                 |

| +24V                                            | 1 Amp Max                                                                 |

| -24V                                            | 1 Amp Max                                                                 |

| User Breadboard Area                            | 82 square inches                                                          |

| I/O Port Configuration                          | 12 X 8-bit                                                                |

| I/O Port Drive Current (TTL Logic Levels)       |                                                                           |

| Sink                                            | 64 mAmp @ 0.55V max                                                       |

| Source                                          | 15 mAmp @ 2.4V min                                                        |

| I/O Port Reset Polarity                         | Logic 1 or logic 0, jumper selectable (JP1)                               |

| I/O Port Operating Modes                        |                                                                           |

| Clocked Input                                   | User supplied clock stores data in port.                                  |

| Buffered Input                                  | Port data sampled during VXIbus read.                                     |

| Latched Output w/Read back                      | Data written during VXIbus write is latched (until subsequent write).     |

| I/O Port Control Signals (x=port number 0 - 11) |                                                                           |

| O/lx                                            | Input/Output selection: O/Ix = 0 selects output,<br>O/Ix =1 selects input |

| LAT/BUFFx                                       | Clocked/Buffered selection: LAT/BUFFx=0                                   |

|                                                 | selects<br>buffered input, LAT/BUFFx=1 selects<br>clocked input           |

| CLKINx                                          | Clock input strobes input data on the rising edge                         |

|                                                 | Note: all control lines are TTL logic level signals                       |

| General Description 1-6                         | EADS North America Defense                                                |

| Parameter                | Specification                                                   |  |

|--------------------------|-----------------------------------------------------------------|--|

| Maximum Module Power     | 6.25 Watts (Does not include user circuits in prototyping area) |  |

| Minimum Airflow          | 0.5 Liters/sec at .04mm $H_2O$ for a 10°C Rise                  |  |

|                          | (See "Module Cooling Considerations" in Section 3)              |  |

| Minimum Airflow, Typical | 2.1 Liters/sec at .20mm H <sub>2</sub> O for a 10°C Rise        |  |

| 20-Watt Application      |                                                                 |  |

### Table 1-4, Cooling Requirements

### Table 1-5, 7064M Mechanical Parameters

| Parameter                                          |                                   | Specificat                                      | ion                              |

|----------------------------------------------------|-----------------------------------|-------------------------------------------------|----------------------------------|

| Enclosure Style                                    | VXI "C" S                         | IZE - Prototype                                 | e Enclosure                      |

| Enclosure Dimensions (in.)                         | 7064M-20                          | X: 14Lx 10.3V<br>X: 14Lx 10.3V<br>X: 14Lx 10.3V | V x 2.4D                         |

| Enclosure weight                                   | 7064M-20<br>7064M-30<br>Note: Sub | erface installed                                | f no Message-<br>d (models -101, |

| Prototype Area Maximum Clearance<br>For Components | Module                            | Circuit<br>Side                                 | Component<br>Side                |

|                                                    | 7064M-<br>10X                     | 0.13 in.                                        | 0.75 in.                         |

|                                                    | 7064M-<br>20X                     | 1.30 in.                                        | 0.75 in.                         |

|                                                    | 7064M-<br>30X                     | 1.30 in.                                        | 1.95 in.                         |

### Table 1-6, 7064M Environmental Specifications

| Parameter                  | Specification                                                               |

|----------------------------|-----------------------------------------------------------------------------|

| Temperature, operating     | 0°C to +55°C                                                                |

| Temperature, non-operating | -40°C to +71°C                                                              |

| Relative Humidity          | 95 +/-5% RH non-condensing; 75+/-5 %RH<br>above 30°C; 45+/-5 %RH above 40°C |

| Altitude, operating        | 10,000 ft                                                                   |

| Altitude, non-operating    | 15,000 ft                                                                   |

| Vibration                  | 0.013" double amplitude, 5-55Hz                                             |

| Fungus resistance          | Yes, fungus inert materials used.                                           |

| Parameter | Specification                                                  |  |

|-----------|----------------------------------------------------------------|--|

| MTBF      | >200,000 Hours, calculated per MIL-HBK217, ground-benign, 30°C |  |

| MTTR      | < 30 minutes                                                   |  |

### Table 1-7, Reliability and Safety Specifications

### Table 1-8, EMC Specifications

|                         | Council Directive 89/336/EEC |

|-------------------------|------------------------------|

|                         |                              |

| EN55011, Group, Class A |                              |

| EN50082-1, IEC801-2,3,4 |                              |

### DEFINITIONS

| EMC     | Electro-Magnetic Compatibility                    |

|---------|---------------------------------------------------|

| MTBF    | Mean Time Between Failure                         |

| MTTR    | Mean Time To Repair                               |

| RH      | Relative Humidity                                 |

| PLCC-XX | Plastic Leaded Chip Carrier Package, XX=Pin Count |

| SO-20L  | Small Outline Package, 20-pin low profile         |

| Model/Option | Part No.      | Description                                                                                                  |

|--------------|---------------|--------------------------------------------------------------------------------------------------------------|

| 7064M-100    | 407620-100    | Single slot master message based prototype module.                                                           |

| 7064M-101    | 407620-101    | Single slot slave message based prototype module without interface installed.                                |

| 7064M-200    | 407620-200    | Double slot master message based prototype module.                                                           |

| 7064M-201    | 407620-201    | Double slot slave message based prototype module without interface installed.                                |

| 7064M-300    | 407620-300    | Triple slot slave master message based prototype module.                                                     |

| 7064M-301    | 407620-301    | Triple slot slave message based prototype module without interface installed.                                |

| 7064M-Opt 05 | 407620-Opt 05 | Message based interface card only.                                                                           |

| 7064M-001    | 407620-001    | Single slot sheet metal enclosure only.                                                                      |

| 7064M-002    | 407620-002    | Double slot sheet metal enclosure only.                                                                      |

| 7064M-003    | 407620-003    | Triple slot sheet metal enclosure only.                                                                      |

| 7064M-Opt 95 | 407620-Opt 95 | Source code for message based interface. Includes manual and source code disks (See Appendix A for Details). |

### Table1-9, Option Table

This page was left intentionally blank.

# Chapter 2 INSTALLATION INSTRUCTIONS

### What's In This Chapter

- Unpacking and Inspection

- VXIbus Logical Address Switch

- VXIbus Interrupt Handler Setting

- Installation into Mainframe

- Self Test Description

- Local Bus Usage

- VXIbus Plug&Play Software Installation

### Unpacking and Inspection

- 1. Remove the 7064M module and inspect it for damage. If any damage is apparent, inform the carrier immediately. Retain shipping carton and packing material for the carrier's inspection.

- Verify that the pieces in the package you received contain the correct 7064M module option and the 7064M Users Manual. Notify EADS North America Defense Test and Services, Inc. if the module appears damaged in any way. Do not attempt to install a damaged module into a VXI chassis.

- 3. The7064M module is shipped in an anti-static bag to prevent electrostatic damage to the module. Do not remove the module from the anti-static bag unless it is in a static-controlled area.

### CAUTION:

ALWAYS PERFORM DISASSEMBLY, REPAIR AND CLEANING AT A STATIC SAFE WORKSTATION.

### VXIbus Logical Address Switch

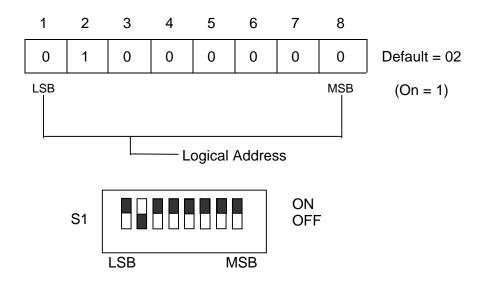

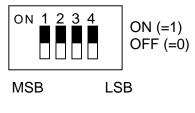

The 7064M Message Based Prototype Module has an internal 8position address DIP switch used to determine the base address of the VXIbus configuration registers. It is located on the top of the module, accessible through the case. Any setting other than 255 indicates static configuration. Refer to VXIbus Specification Revision 1.4 for details.

Figure 2-1, VXIbus Logical Address Switch

Dynamic configuration is an optional alternative method of assigning logical addresses to VXIbus devices, and is defined in detail in Section F of the VXIbus System Specification Revision 1.4. In the ON position, the switch is set to logical 1, and in the OFF position to a logical 0. The user can select any logical address from 1 to 254 for static configuration.

#### NOTE:

Logical address 0 is not allowed. Set logical address to 255 for dynamic configuration.

|                                     | NOTE:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                     | The 7064M Message Based Breadboard Module is shipped with the logical address set for 2. Refer to the Resource Manager's manual for details about addressing methods.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| VXIbus Interrupt<br>Handler Setting | One programmable interrupt line is provided on the 7064M module.<br>This line is assigned by using the <i>assign interrupter line</i> word serial<br>protocol command (See Page 182 of Section E, Revision 1.4 of the<br>VXIbus Specifications). The <i>Int_ID</i> is set to 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 7064M to VXIbus<br>Mainframe        | The 7064M module is ready for operation when shipped. The address switch is set to 2.<br>To install the 7064M in a C-size VXI chassis, use the following                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| Installation                        | instructions:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|                                     | 1. Ensure power is OFF.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                                     | <ol><li>Configure the interrupt daisy chain on the backplane<br/>to bypass empty slots, per VXIbus specifications.</li></ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                                     | <ol> <li>Remove the front cover of the VXI chassis, and slide<br/>the 7064M into the appropriate slot with the LED's<br/>towards the top (or to the left when using a horizontal<br/>chassis).</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|                                     | To ensure reliable VXlbus communications when using 7064M "slave" modules without a VXlbus communications interface (i.e., 7064M-101, 7064M-201, and 7064M-301 series), the user must note the following. The VME Specification requires that the Interrupt Acknowledge (IACK) and BUSGRANT (BG) signal lines be daisy-chained from slot-to-slot across the backplane. This means that for each slot the BUSGRANT and IACK signals are input on Row A of the P1 connector and output on Row C of the P1 connector. When there is no VXlbus interface installed in the 7064M module, the user must ensure that these signals are passed onto the next slot. There are three ways this can be done, depending on the backplane installed in your VXlbus chassis. You will need to consult the chassis manual to verify the type of backplane you have. |  |

- VXIbus Backplanes with Bus Grant and Interrupt Acknowledge DIP Switches. - The user must close the switches in the slot where the 7064M will be installed. (Example: 1264A, 1261).

- 2. VXIbus Backplanes with Active Automatic Daisy-Chain. -The Bus Grant and Interrupt Acknowledge signals will be automatically passed to the next slot. (Example: 1261B, 1269 chassis).

- 3. VXIbus Backplanes with Auto-Configuration P1 Connectors. - With this style of connector, the BUSGRANT and IACK daisy-chains are broken as soon as the module is installed in a slot. The user must reconnect the daisy-chain in the 7064M module. This is done by shorting the pins on the P3 or J101 connector as shown in Table 2-1 below (Example: 1261AH, 1261A+, 1261AM chassis).

#### Table 2-1, Signal Shorts For Chassis With Auto-Configuration P1 Connectors

| SIGNAL               | P3 or P101 SHORT             |

|----------------------|------------------------------|

| BG0IN* and BG0OUT*   | Pin 4 Row B to Pin 5 Row B   |

| BG1IN* and BG1OUT*   | Pin 6 Row B to Pin 7 Row B   |

| BG2IN* and BG2OUT*   | Pin 8 Row B to Pin 9 Row B   |

| BG3IN* and BG3OUT*   | Pin 10 Row B to Pin 11 Row B |

| IACKIN* and IACKOUT* | Pin 21 Row A to Pin 22 Row A |

### Power-Up Self-Test Initialization

Before turning on the VXIbus mainframe, make sure a Slot 0 with a Resource Manager is present. Upon power-up of the system, the 7064M goes through the following power-up sequence:

- The 7064M breadboard module has two LED's on the front panel - FAIL and ACCESS. The LED functions are:

- FAIL On during a self-test

Off when the self-test has successfully completed

ACCESS Blinks on when the VXlbus is accessing the module's logical address

At power-up, the 7064M goes through a series of operations to ensure proper initialization and establish the proper start-up state. A brief description of this power-up sequence follows.

| Self-Test                                   | Tests are performed on ROM, RAM, Non-Vol and the timer to ensure they are operating correctly.                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Board ID Check                              | Each breadboard may have one or more board ID bytes selected by<br>the user. The user selects a port, a value and a mask if necessary.<br>This information is stored into Non-vol by the user and verified<br>during the power-up sequence.                                                                                                                                                                                             |

| Port Initialization                         | All I/O ports configured as outputs are initialized to either all 0's or all<br>1's during system reset (jumper selectable on each breadboard).<br>The user can also specify initial values for ports and have them<br>stored in Non-vol. If any of these values have been specified, they<br>are set at this point in the power-up sequence. The operation of the<br>board ID is described in more detail in Section 3.                |

| VXIbus Interface<br>Initialization          | At times, it may be desirable for the user to specify an initial value for<br>one or more of the VXIbus registers. For example, the user specifies<br>a model code. This requires the new model code to be placed in the<br>"device-type" VXIbus register. The user can specify these values<br>and have them stored in Non-Vol. If any of these values have been<br>specified, they are set up at this point in the power-up sequence. |

| Local Bus Usage<br>with 7064M<br>Breadboard | The VXIbus has a provision for interconnecting adjacent cards through a local bus. The bus consists of 12 lines which jumper cards together. A card on the left of another will have connections on the "C" side of P2 tied to the "A" side of P2 for the card to its right.                                                                                                                                                            |

### Slave Module with 7064M Master Module

NOTE:

Master module has an option 5 control card mounted. Slave module does NOT have an option 5 control card mounted and must be installed in the chassis to the right side of the Master module.

The Master and Slave module should always have the following pads jumpered with 22 gage jumper wire:

J3 J4 LB0 \_\_\_\_\_ LB1 \_\_\_\_\_ LB2 \_\_\_\_\_ LB3 \_\_\_\_\_ LB4 \_\_\_\_\_ LB5 \_\_\_\_\_ LB6 \_\_\_\_\_ LB7 \_\_\_\_\_ LB8 \_\_\_\_\_ LB9 \_\_\_\_\_

The Slave module must be the next card on the right of the Master module. When a Slave module is used with a Master module the following jumpers must be installed on the Master module. Use 22 gage jumper wire.

J5 J6 LB0 \_\_\_\_\_ LB1 \_\_\_\_\_ LB2 \_\_\_\_\_ LB3 \_\_\_\_\_ LB4 \_\_\_\_\_ LB5 \_\_\_\_\_ LB6 \_\_\_\_\_ LB7 \_\_\_\_\_ LB8 \_\_\_\_\_ LB9 \_\_\_\_\_

The same jumpers should be installed on the Slave module if multiple Slave modules are installed with the exception of the last Slave module.

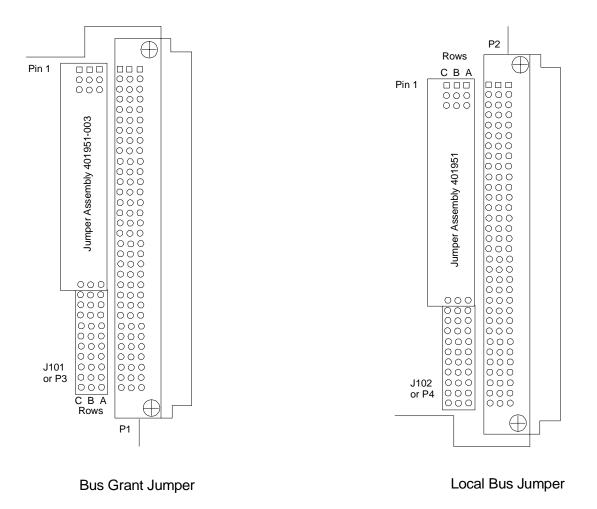

### Bus Grant and Local Bus Jumpers

The Slave module must always have the Bus Grant and Local Bus jumper boards plugged into J3 and J4.

Bus Grant (Part Number 401951-003) has been designed to perform this task and may be ordered from the EADS North America Defense Test and Services, Inc. Parts Department. The jumper should be located in P3 or J101, pins 1 through 22 as shown in **Figure 2-1**. For Slave module operation 401951-003 must be plugged into the P3 connector.

Local Bus Jumper (401951) should be plugged into J102 or P4 connector.

Figure 2-2, Installation of Bus Grant Jumper and Local Bus Jumper

### Installing the VXI*plug&play* Software

After the 7064M been installed into the VXI mainframe, the VXI*plug&play* software may be used to communicate with the 7064M. To install the software, first power on the mainframe, then perform the following operations:

- 1. Start Windows (3.1, 95, or NT) on your computer if it is not already running.

- 2. Insert the appropriate (Windows 3.1 or 95/NT) VXI*plug&play* installation disk #1 into the 3-1/2" floppy disk drive.

- 3. Run the SETUP program on the installation disk.

- 4. Follow the instructions presented by the SETUP program.

After the SETUP program has completed, the executable Soft Front Panel program may be run. To run the soft Front Panel, ensure that the following conditions are met:

- 1. The computer is connected to the VXI mainframe via a MXI/VXI interface, a GPIB/VXI interface, or the computer is an embedded VXI computer.

- 2. VISA is loaded onto your system. VISA is a library of functions which provide communication between a computer and instruments (GPIB and VXI). VISA may be obtained from the manufacturer of the MXI/VXI, GPIB/VXI, or embedded computer.

- 3. The VXI mainframe has power applied and the power switch has been turned ON.

- 4. For the MXI/VXI and embedded computers, the resource manager program has been run since the VXI mainframe power was last turned ON.

To run the Soft Front Panel, "double-click" on the 7064M Front Panel" icon in the "VXIPNP" Windows Group.

If the four conditions above are met, the Soft Front Panel program will automatically locate the 7064M in the Mainframe. The Soft Front Panel program will display the VXI logical address of the 7064M and the "Active" LED on the Soft Front Panel will be green.

## Chapter 3 USING THE BREADBOARD

### What's In This Chapter

This chapter provides information as follows:

- Module cooling considerations and operating point calculations.

- Connection points for signals and power used to interface to the user development area.

- Card address switch settings.

- Software commands to allow user control of circuits in the user development area.

### Module Cooling Considerations

VXI modules are specified to require a particular airflow to maintain a specific temperature rise, which is typically 10° Celsius. The airflow and back-pressure (pressure change across the module) values determine a single operating point that may be plotted on a VXI mainframe cooling curve. If the operating point lies under the mainframe cooling curve, there is a high probability that the module will remain within its specified temperature rise. If the operating point is above the mainframe cooling curve, the temperature rise of the module may exceed the specified value.

### Calculated Module Operating Point

A calculation of the operating point or cooling requirements for the 7064M (and user circuitry) can be determined if the total power dissipation is known. This is detailed below.

#### CAUTION:

### A module with hot spots or airflow restrictions may require increased airflow. Refer to the VXIbus Specification Revision 1.4 for details.

To calculate the module operating point:

- Determine the desired maximum temperature rise allowed across the module. It is typically 10°C, but may be higher or lower depending on the specified operating environment, function of the module, part sensitivities, etc.

- 2. Determine the maximum power in watts dissipated inside the module (P<sub>6.25 WATTS</sub> + P<sub>USER CIRCUITRY</sub>).

- 3. Determine the airflow required by the module to maintain the desired temperature rise. In most cases, this is calculated from the power dissipated, desired temperature rise, and the specific heat of air. (For a 10°C rise, airflow in L/S=0.08 \* power in watts.) The required airflow may be increased or decreased depending on hot spots, airflow blockages, etc.

- 4. Determine the pressure drop across the module when the specified airflow (in L/S) is forced through the module. A reasonable estimate may be calculated from the equation for a typically dense VXI module: P=0.02G<sup>2</sup> + 0.05G. (P is pressure in mmH<sub>2</sub>O and G is airflow in liters per second.)

- 5. Plot the module operating point (P, L/S) on the mainframe curve. If the module operating point lies under the mainframe cooling curve, the module should remain within its specified temperature rise.

### DC Voltages Available to Prototyping Area

The 7064M Message Based Prototype module provides filtered and fused VXI supply voltages on the board. The user can access these voltages for his prototyping circuitry. The VXI voltages available are listed below in **Table 3-1**.

| Voltage | Max Current | Fuse | User Access Point |

|---------|-------------|------|-------------------|

| +5V     | 5Amps Max   | 10A  | +5VA              |

| +12V    | 1Amp Max    | 2A   | +12VA             |

| +24V    | 1Amp Max    | 2A   | +24VA             |

| -5.2V   | 5Amps Max   | 10A  | -5.2VA            |

| -2V     | 2Amps Max   | 5A   | -2VA              |

| -12V    | 1Amp Max    | 2A   | -12VA             |

| -24V    | 1Amp Max    | 2A   | -24VA             |

### Table 3-1, DC Voltages Available to Prototyping Area

Note: All fuses are Littlefuse 255 Series or equivalent.

+5V and Ground are distributed throughout the prototyping area. Refer to **Figure 3-1** for connection points for other VXI voltages. There are 77 +5V/Ground power pads throughout the prototype area. A connection to the VXI Chassis is provided the center standoff located in the development area. Connect the feed-through at the center standoff to the adjacent "GND" feed-through to make the "Chassis" to "Logic" ground connection.

### Local Bus Interface

Direct access to the VXI Local Bus is provided on the 7064M Message Based Prototype Module. The VXI Local Bus allows communication between modules in adjacent slots of a VXI chassis. Local Bus "A" is connected to the module on the left, while Local Bus "C" is connected to the module to the right. The user should exercise caution when using the Local Bus to ensure module to module compatibility. Refer to VXI Rev. 1.4 Section B6.2.6 and B7.3.7 for further explanation of the VXI Local Bus. Connections are provided as follows on the 7064M:

| 7064M Signal | VXI Local bus Signal |

|--------------|----------------------|

| J5 pin LB0   | Local Bus C0         |

| J5 pin LB1   | Local Bus C1         |

| J5 pin LB2   | Local Bus C2         |

| J5 pin LB3   | Local Bus C3         |

| J5 pin LB4   | Local Bus C4         |

| J5 pin LB5   | Local Bus C5         |

| J5 pin LB6   | Local Bus C6         |

| J5 pin LB7   | Local Bus C7         |

| J5 pin LB8   | Local Bus C8         |

| J5 pin LB9   | Local Bus C9         |

| J5 pin LB10  | Local Bus C10        |

| J5 pin LB11  | Local Bus C11        |

|              |                      |

| J101 pin 5   | Local Bus A0         |

| J101 pin 6   | Local Bus A1         |

| J101 pin 8   | Local Bus A2         |

| J101 pin 9   | Local Bus A3         |

| J101 pin 11  | Local Bus A4         |

| J101 pin 12  | Local Bus A5         |

| J101 pin 14  | Local Bus A6         |

| J101 pin 15  | Local Bus A7         |

| J101 pin 17  | Local Bus A8         |

| J101 pin 18  | Local Bus A9         |

| J101 pin 20  | Local Bus A10        |

| J101 pin 21  | Local Bus A11        |

Table 3-2, VXI Signals

### TTL Trigger Lines

The 7064M Message Based Prototype Module provides direct access to the VXI TTL Trigger lines. These lines are typically used for intermodule communication applications such as trigger, handshake, clock, or logic state transmission. They are open collector active low signals and are pulled high (inactive) by the VXI backplane. Several standard communication protocols are defined by VXI Rev. 1.4. Refer to section B6.2.3 of the VXI Rev. 1.4 specification for further details. The TTL Trigger connections are defined below.

| E-Point | Signal Name |

|---------|-------------|

| E6      | TTLTRG0-    |

| E7      | TTLTRG1-    |

| E8      | TTLTRG2-    |

| E9      | TTLTRG3-    |

| E10     | TTLTRG4-    |

| E11     | TTLTRG5-    |

| E12     | TTLTRG6-    |

| E13     | TTLTRG7-    |

### Table 3-3, VXI TTL Trigger Lines

### Miscellaneous VXI Signals

The 7064M provides direct access to various VXI defined signals. Details of each of these signals can be found in the VXI Rev. 1.4 specifications. Connections to these signals are as follows.

### Table 3-4, Miscellaneous Signals

| Signal Name      | E-Point |

|------------------|---------|

| ACFAIL-          | E27     |

| SERCLK           | E4      |

| SERDAT-          | E5      |

| CLK10+           | E4      |

| CLK10-           | E5      |

| SUMBUS           | E26     |

| BERR-            | E41     |

| +5VSTDBY         | E1      |

| SYSRESET-        | E3      |

| SYSCLK(buffered) | E49     |

### I/O Port Write Strobes

The 7064M provides direct access to the I/O port "write" strobes. These signals are used by the message-based interface to clock data into ports when configured as outputs. The signals are driven by HCT00 nand gates.

| Port # | E-Point |

|--------|---------|

| 0      | 14      |

| 1      | 15      |

| 2      | 16      |

| 3      | 17      |

| 4      | 18      |

| 5      | 19      |

| 6      | 20      |

| 7      | 21      |

| 8      | 22      |

| 9      | 23      |

| 10     | 24      |

| 11     | 25      |

### Table 3-5, I/O Port Write Strobes

### Input/Output Ports

The 7064M breadboard has twelve 8-bit ports (refer to **Figure 3-1**). Each Port can be individually configured for input or output. Three lines are supplied for the user to control the type of port and its operation. The port outputs are designed to accept a 14-pin dual row (0.10 inch spacing) connector for the user to easily wire into the breadboard area.

| Table 3-6, I/O Port Description for Port 0 to Port 11 |  |

|-------------------------------------------------------|--|

|-------------------------------------------------------|--|

| Signal<br>X = 0 to 11 | Port x Pin<br>X = 0 to 11 | Туре    | Description                                                                                                                                                                                                                                                                                                   |

|-----------------------|---------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| O/lx!                 | 1                         | Control | Along with LAT/BUFFx! controls the operational mode of the port.                                                                                                                                                                                                                                              |

| +5VA                  | 2,6                       | Power   | Fused +5V Power                                                                                                                                                                                                                                                                                               |

| CLKINx                | 3                         | Control | Used to clock data into the port when the<br>port is configured as a clocked input. A<br>rising edge on this line clocks data into<br>the port. Once clocked in, the data can be<br>read over the VXIbus. If the port is<br>configured as a buffered input, this line<br>has no effect on the port operation. |

| GND                   | 4                         | Power   | Logic Ground                                                                                                                                                                                                                                                                                                  |

| Signal<br>X = 0 to 11 | Port x Pin<br>X = 0 to 11 | Туре    | Description                                                                                                                                                                                                                                                                                           |

|-----------------------|---------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LAT/BUFFx!            | 5                         | Control | Used to configure an input port as either<br>a clocked input or a buffered input. When<br>the LAT/BUFFx! line is held low, the input<br>port functions as a buffered input. When<br>the LAT/BUFFx! line is held high, the<br>input port functions as a clocked input.                                 |

| I/Ox(07)              | (7 to 14)                 | IN/OUT  | The I/Ox (07) Signals comprise an 8-bit<br>data/control port used to interface to the<br>breadboard area. Note that "x" refers to<br>ports 0 to 11. The twelve I/O ports can be<br>configured in three ways:<br><u>Clocked Inputs</u> – The user<br>supplies a clock signal that stores               |

|                       |                           |         | data in the port.<br><u>Buffered Input</u> – Data on the input<br>lines are read when the port is<br>read from the VXIbus.<br><u>Latched Output with Readback</u> –<br>Data written to an output port<br>through the VXIbus is held on the<br>I/O lines until a subsequent write<br>changes the data. |

| Controlling the<br>I/O Ports | Control of user-defined circuitry in the breadboard area is accomplished through the use of the 96 buffered I/O lines available on the breadboard card.                                                                                                                                                                                                |  |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                              | A set of local commands is available to the user to allow for the control of the user-defined circuitry through the twelve I/O ports available.                                                                                                                                                                                                        |  |

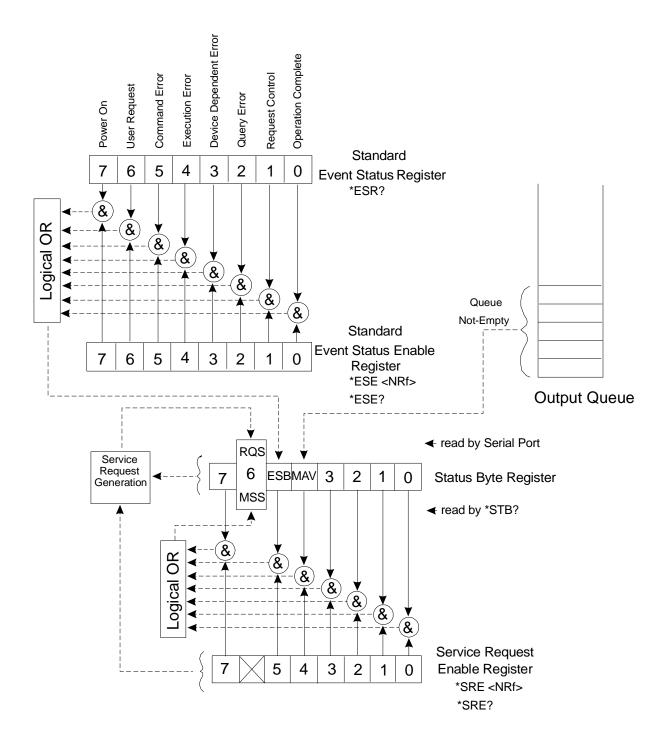

|                              | When a command is sent to the 7064M using word serial protocol, it<br>is received and parsed by the command parser. If the command<br>matches a command from the local command set (See Page 3-11),<br>the appropriate routine is called. If no matching command is found,<br>bit 3 in the standard Event Status Register is set to indicate an error. |  |

| Output Port<br>Reset Polarity | <ul> <li>All outputs are set to a known level during reset. The user can select whether all the outputs will be set to a logic 1, or all outputs will be set to a logic 0 by simply doing the following:</li> <li>To cause all outputs to be set to a logic 1 during reset, connect pin 1 to pin 2 on JP1 of the breadboard card (See Drawing No. 405124 for the location of JP1).</li> <li>To cause all outputs to be set to a logic 0 during reset, connect pin 2 to pin 3 on JP1.</li> </ul>                               |  |  |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                               | NOTE:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                               | The 7064M breadboard module is shipped with connections on JP1 set to clear all ports to a logic 0 during reset. JP1 has no effect on ports configured <i>for input.</i>                                                                                                                                                                                                                                                                                                                                                      |  |  |

|                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| I/O Port                      | The 7064M I/O ports can be configured in three ways:                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| Configuration                 | <ul> <li><u>Clocked Inputs</u> - The user supplies a clock signal that stores<br/>data in the port. At a later time, the port can be read from the<br/>VXIbus.</li> </ul>                                                                                                                                                                                                                                                                                                                                                     |  |  |

|                               | <u>Buffered Inputs</u> - Data on the input lines is read when the port is read from the VXIbus. No clock signal is required.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|                               | • <u>Latched Output with Readback</u> - Data written to an output port through the VXIbus is held on the data lines until another write changes the data.                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| I/O Port Control              | There are two lines that control the configuration of an $I/O - O/Ix!$ and LAT/BUFFx!, where x is the associated port number (0 to 11):                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|                               | • The O/Ix! line: Used to configure the port as an input or an output. When the O/Ix! line is held low, the port functions as an input. When the O/Ix! line is held high, the port functions as an output.                                                                                                                                                                                                                                                                                                                    |  |  |

|                               | • LAT/BUFFx! line: Used to configure an input port as either a clocked input or a buffered input. When the LAT/Buffx! line is held low, the input port functions as a buffered input. When the LAT/Buffx! line is held high, the input port functions as an clocked input. If the port is configured as an output, this line should be held low (configured as a buffer). The data latched on the output can then be read back with a read from the VXIbus. This allows bit operations which modify a single bit, leaving the |  |  |

other bits in a port unchanged.

| Table 3-7, I/C | Port Control |

|----------------|--------------|

|----------------|--------------|

| O/Ix! | LAT/BUFFx! | OPERATION                       |

|-------|------------|---------------------------------|

| 0     | 0          | Buffered Input                  |

| 0     | 1          | Clocked Input                   |

| 1     | 0          | LatchedOutput With<br>Read Back |

| 1     | 1          | Not Recommended                 |

#### NOTE:

These two control lines do not have to be static. They can be connected to data pins on an output port, or they can be connected to some user control lines. This allows ports to be used for bi-directional communication, or other more complex functions.

There is one line that is used as a clock line, where x is the associated port number (0 to 11):

• CLKINx line: Used to clock data into the port when the port is configured as a clocked input. A rising edge on this line clocks data into the port. Once clocked in, the data can be read over the VXIbus. If the port is configured as a buffered input, this line has no affect on the port operation.

NOTE:

The 7064M breadboard is shipped with the I/O ports configured for Latched Output with Readback as the default mode.

## Module Address Switch

The card addresses can be offset from the default (zero) by setting the card address switch found on the left side (viewed from the front) of the module. This four pin DIP switch modifies the card address to be used with the local command set. Refer to **Table 3-8** for a description of the switch.

| SWITCH |   | Card Address | Port Address |              |         |       |

|--------|---|--------------|--------------|--------------|---------|-------|

| 1      | 2 | 3            | 4            | Caru Audress | Fort Ad | uless |

| 0      | 0 | 0            | 0            | 0            | 0       | 2047  |

| 0      | 0 | 0            | 1            | 1            | 2048    | 4095  |

| 0      | 0 | 1            | 0            | 2            | 4096    | 6140  |

| 0      | 0 | 1            | 1            | 3            | 6141    | 8191  |

| 0      | 1 | 0            | 0            | 4            | 8192    | 10239 |

| 0      | 1 | 0            | 1            | 5            | 10240   | 12287 |

| 0      | 1 | 1            | 0            | 6            | 12288   | 14335 |

| 0      | 1 | 1            | 1            | 7            | 14336   | 16383 |

| 1      | 0 | 0            | 0            | 8            | 16384   | 18431 |

| 1      | 0 | 0            | 1            | 9            | 18432   | 20479 |

| 1      | 0 | 1            | 0            | 10           | 20480   | 22527 |

| 1      | 0 | 1            | 1            | 11           | 22528   | 24575 |

| 1      | 1 | 0            | 0            | 12           | 24576   | 26623 |

| 1      | 1 | 0            | 1            | 13           | 26624   | 28671 |

| 1      | 1 | 1            | 0            | 14           | 28672   | 30719 |

| 1      | 1 | 1            | 1            | 15           | 30720   | 32767 |

#### Table 3-8, Card Address Switch

Default = 0

Figure 3-2, Card Address Switch

| Port Addressing | There are two types of addressing used in port commands: |

|-----------------|----------------------------------------------------------|

| Schemes         | - port addressing                                        |

- card-relative port addressing